CPUについて、最新の世代やらスペックなどを調べていると、

- 「インテルは10nmプロセスに大苦戦。」

- 「AMDのCPUとグラボは遂に7nmプロセスに進出。」

という具合に、ナノメートル単位でCPUの凄さを表現している記事やサイトが見られる。本記事では「nmって、CPUの何の長さや大きさを示すんだろう?」という人向けに、プロセスルールを分かりやすく図解してみる。

プロセスルールとは何か?

日本では「プロセスルール」と呼ばれているが、海外では「Process Size」(プロセスサイズ)という呼び方がよく使われています。ルールよりもサイズの方が、表現としては分かりやすい。

プロセスは「製造」という意味を持ち、サイズはそのまま「大きさ」という意味がある。直訳すれば、製造の大きさ。つまり「CPUをどれだけ細かく製造しているか?」を示すのがプロセスルールということ。

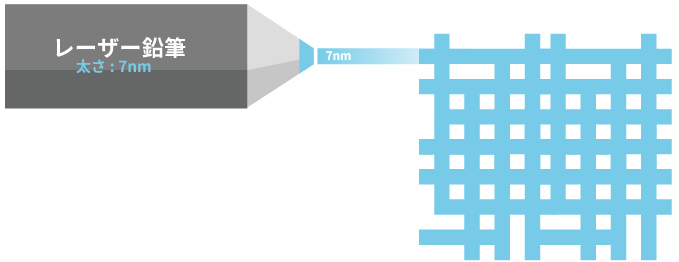

具体的には「配線の太さ」とイメージする

「細かく製造する」では、まだイメージしにくい。もっと具体的なイメージに変換すると、CPUを設計通りに配線する時に使う、配線の太さだと思ってください。

AMDやインテルなどのCPUメーカーは、まず設計図(チップのデザイン)を作成します。設計図には膨大な数※の回路パターンが記されており、回路のパターンによってCPUや内蔵グラフィックス、そしてキャッシュなど。役割分担が変わってくる。

回路のパターンによって機能が変わるというのは、人間の最小単位が細胞でも、細胞同士の結びつき方によって内臓の機能が違うのと似ています。

※ CPUの場合は数十億個、グラボの場合は100億個を超える膨大なパターンが描かれている。

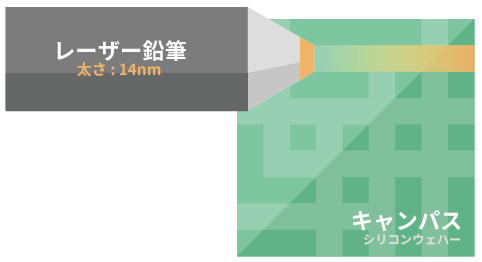

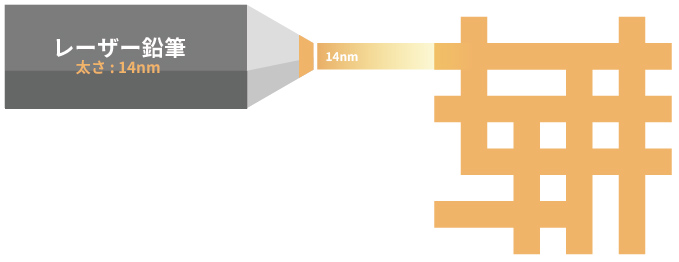

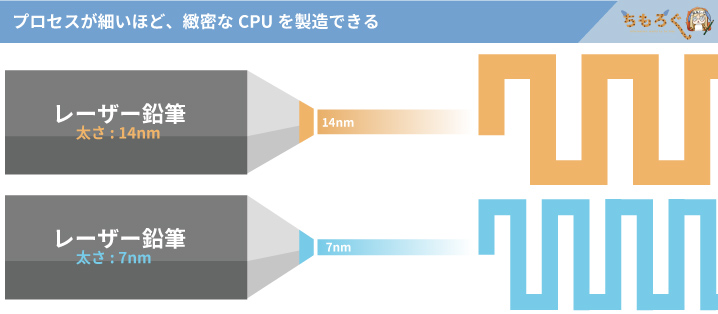

さて、設計図が完成したら、後は設計図に記されているパターン通りにCPUを製造する。製造というよりは、印刷と言った方が分かりやすい。ものすごくザックリと言えば、CPUの製造はキャンパスの上に鉛筆を使って回路パターンを描くだけですから。

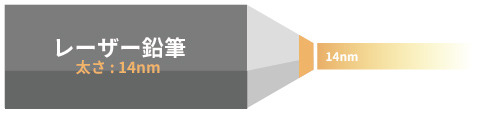

現在はレーザー鉛筆(ArFエキシマレーザー)を使って、回路パターンを印刷(=配線)していく。プロセスルールとはまさに、このレーザー鉛筆の先端の太さをことを示す。

14nmの太さの鉛筆を使えば、14nmが配線の最小単位になる。鉛筆の太さが14nmである以上、それよりも細い線で印刷(=配線)はできません。

プロセスが細いほど、細かい設計が出来る

ここまでの解説で、「プロセスルールとはCPUの製造に使う、レーザー鉛筆の細さ」のこと。という理解ができたはず。つまりレーザー鉛筆の先端が細ければ細いほど、よりきめ細やかな製造が出来るようになる。

では、次は細かい設計と製造が出来るようになると、どのようなメリットがあるのかを解説していく。メリットが分かってしまえば、「7nmに到達、スゴイ!!」といった解説の意味がグッと分かりやすくなりますよ。

プロセスルールの微細化とメリット

同じ面積で、より大量のトランジスタを描くことができる

CPUの設計図に描かれている回路パターンは、基本的にはトランジスタの配置情報です。たとえば、Ryzen 7 2700Xは約48億個のトランジスタが、Apple A12は約69億個のトランジスタの配置情報が描かれている。

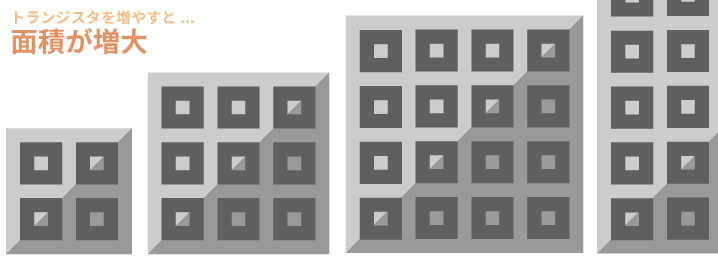

そして(単純に言えば)トランジスタが多いほど、CPUの処理性能は高くなる。かと言って、性能のためにトランジスタを詰め込めば詰め込むほど、大量の面積が必要になってしまう。

そこで解決策が「プロセスルールの微細化」です。製造に使うレーザー鉛筆の先端を、もっともっと細くすれば、同じ面積のキャンパスに大量のトランジスタを描くことが可能になります。

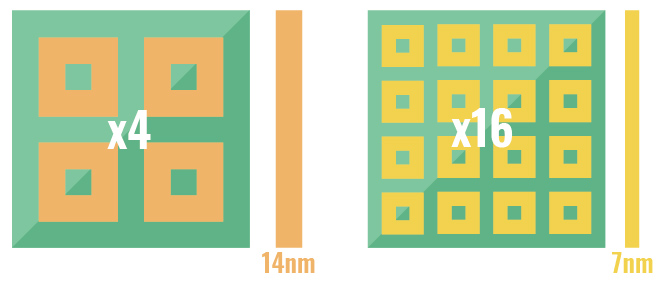

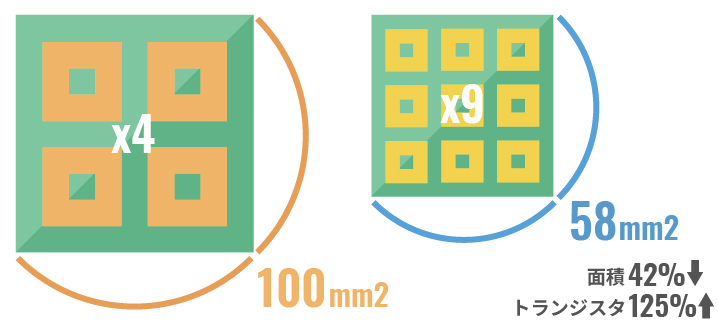

分かりやすく図解するとこの通り。14nmプロセスだと、トランジスタを4個しか描けません。しかし、半分の7nmプロセスに切り替えると、同じ面積なのに描けるトランジスタ数は16個に増加します。

- 14nm:トランジスタを4個しか描けない

- 7nm:トランジスタを16個も描ける

配線の太さが半分になっただけで、面積あたりのトランジスタ数は4倍にも増加してしまった。このことから、プロセスルールの微細化がCPUの性能とコスパを高める上で、非常に重要だということが理解できる。

| プロセスルール | トランジスタの大きさ | 同じ面積のトランジスタ数 |

|---|---|---|

| 100% | 100% | 1.0 個 |

| 90% | 81% | 1.2 個 |

| 80% | 64% | 1.6 個 |

| 70% | 49% | 2.0 個 |

| 60% | 36% | 2.8 個 |

| 50% | 25% | 4.0 個 |

| 40% | 16% | 6.3 個 |

| 30% | 9% | 11.1 個 |

| 20% | 4% | 25.0 個 |

| 10% | 1% | 100 個 |

| 5% | 0% | 400 個 |

| 2.5% | 0% | 1600 個 |

| 1.25% | 0% | 6400 個 |

プロセスルールが70%に縮小すると、トランジスタ数は2倍に。50%へ半減すると、トランジスタは一気に4倍になる。

参考までに、初代Pentium(800nmプロセス)のトランジスタ数は310万個。Core i7 6950X(14nmプロセス)は32億個です。面積あたりのトランジスタ数を求めると、約1230倍になっており、計算はだいたい合っています。

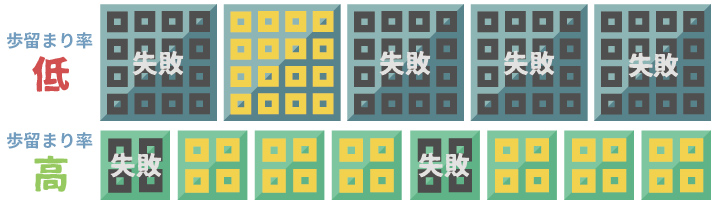

歩留まり率が向上して、コスパが改善する

性能のためにトランジスタを詰め込めば詰め込むほど、大量の面積が必要になってしまう。

次はこの一文について、深掘りする。CPUの性能はトランジスタが多いほど良くなるけれど、トランジスタをたくさん載せようと思えば、大量の面積が必要になるのは明白ですよね。

では、大量の面積が必要になると何が問題なのか。端的に言うと、CPU1個あたりの製造コストが高くつくようになる。CPUは面積が大きいほど、「良品」を製造するのが難しくなるのです。

そして、良品がどれくらい出てくるかの割合を「歩留まり率」と言う。プロセスルールを微細化して設計を細かくすることで、より少ない面積で高性能を目指せるようになる。

だからプロセスルールの微細化は、性能アップをしつつ歩留まり率の向上を両立できる。

更に、チップ1枚あたりの面積が小さくなれば、同じ量のシリコンウェハー(=CPUの原材料)からよりたくさんのCPUが採れるようにもなる。微細化は確実にコスパを改善する効果があります。

性能だけでなく、消費電力も改善してしまう

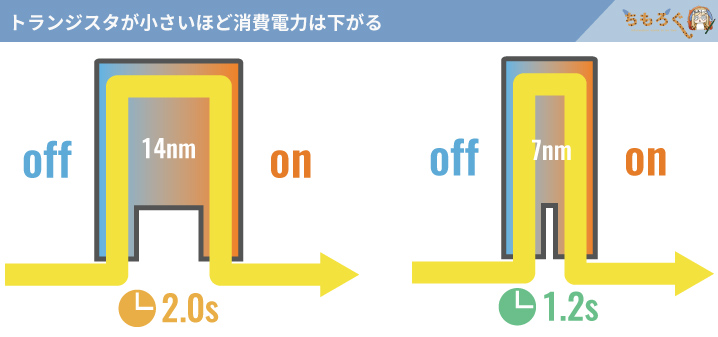

プロセスルールの微細化というと性能だけに目が行くが、実は消費電力を改善する傾向もある。なぜなら、トランジスタが小さくなればなるほど、トランジスタを動かすのに必要な電力が減るからです。

わかりやすさを重視して図解すると、こんなイメージ。

トランジスタは電気が通っている状態(on状態)と、電気が通っていない状態(off状態)を繰り返している。これをスイッチングと呼び、トランジスタが大きいとスイッチングに時間が掛かってしまいます。

スイッチングに掛かっている時間が長いほど、使っている電力も多くなる。だから、プロセスルールの微細化でトランジスタが小さくなると、スイッチングに掛かる時間が縮小されるため、結果的に消費電力を減らせるというわけ。

消費電力あたりの性能(マルチスレッド)

14nm22nm32nm45nm

プロセスの縮小に成功するごとに、消費電力あたりのマルチスレッド性能は向上しています。14nm以降はプロセスの縮小が滞っていて、コア数の増量や冷却性能の向上で何とか…凌いでいる現状です。

結論、プロセスルールは小さいほど良い

基本的に、プロセスルールの微細化はメリットの方が遥かに多いことが、ここまでの解説で分かりました。

プロセス微細化のメリット- より高性能なCPUを製造できる

- コストパフォーマンスを改善できる

- 消費電力を抑えることもできる

傾向として、より小さいプロセスルールで製造されたCPUほど、高性能かつ省電力になりやすい。だからプロセスルールの微細化は、CPUの性能アップを狙う上で「王道の手法」と言って良いです。

【参考】プロセスの微細化(世代更新)による性能変化

実際のところ、プロセスルールの微細化に成功することで、CPUの性能がどれくらい進化してきたのか。データで知りたい人は、こちらの記事を読んでみてください。

驚くほど進化しています。

プロセスルールの「よくある勘違い」

ここまで「プロセスルールとは何か?」と、微細化のメリットについて解説してきた。ただ、初心者向けにかなり簡略化しているので、注意したい点について。少しだけ補足的な解説を行います。

実はメーカーによってプロセスルールのサイズ感が違う

初心者向けに、ものすごくザックリまとめると以下のように覚えておけばOK。

- インテルがもっとも細かい

- それ以外はインテルより一回り大きい

これだけ覚えておけば大丈夫。

詳しい解説は端折りますが、インテルがCPUの製造に使うプロセスルールは、細かいだけでなく「密度」も凄まじい。カンタンに言えば、「線」が細いだけでなく、線同士の「間隔」もギチギチに詰まっているのです。

対して、競合他社(TSMC、GLOBALFOUNDRIES、Samsung)はインテルより「密度」が緩い。

| メーカー | プロセス | 配線密度 | 難易度 | ||

|---|---|---|---|---|---|

| インテル | 10nm | GP : 54nm | FP : 34nm | MP : 36nm | 高 |

| GF | 7nm | GP : 56nm | FP : 30nm | MP : 40nm | 普通 |

| TSMC | 7nm | GP : 54nm | FP : – | MP : 40nm | 普通 |

| Samsung | 7nm | GP : 54nm | FP : 27nm | MP : 36nm | 高 |

配線密度という観点から見ると、競合他社の言っている「7nm」は、インテルの言っている「10nm」とだいたい同じということが分かる。

インテル以外のメーカーが発表しているプロセスルールは、数字のまま受け止めずに、1サイズ大きいと思っておこう。「7nmなら10nmくらい、10nmなら14nmくらいだな。」という感覚。

※国際半導体技術ロードマップによれば「最小配線ピッチの50%」を微細化の指標として扱う、と定められている(資料)。

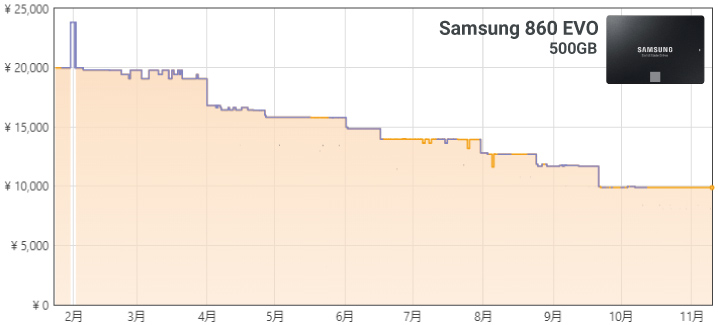

微細化してすぐ、価格が安くなることはない

新しいプロセスルールでCPUを製造できる設備(=ファブ)に掛かる初期投資は、だいたい数千億円~1兆円を超えてしまう。CPUを作る装置が1個あたり100億円だったりするので、とにかく金がかかる。

だから、プロセスルールの微細化に成功したからと言って、すぐにコストパフォーマンスが劇的に改善することはない。初期投資を回収するという意味で、その分のコストが価格に転嫁されます。

たとえばサムスンのSSDが分かりやすい実例。新しい設備でSSDの製造を開始して、数ヶ月経ってから急に値下がりを始めたりするが、設備投資のコストを回収し終えたのが主な要因だったりする。

まとめ:プロセスルールはCPU製造の細かさ

というわけで、本記事の解説でプロセスルールが「CPUの製造に使われるレーザー鉛筆の細さ」であること、「プロセスが細かいほどCPUの性能が高くなる」ということが分かったと思います。

1971年にインテルが発表したCPUのプロセスルールは「10000nm」でした。それから約50年が経過し、現在はわずか0.14%にあたる「14nm」まで微細化された。

約714倍も、今のCPUは緻密です。別の言い方をすれば、同じ面積で51万倍ものトランジスタを載せられる。クロック周波数は6000倍以上に進化し、性能は100万倍以上も違う。

微細化に限界がやってきた感はある

ただ、最近のCPU界はだんだんプロセスルールの微細化が遅くなっている。インテルは2014年以降、そろそろ5年間も「14nm」プロセスを使い続けています。

「10nm」プロセスの生産がまったく上手く行かず、延期に延期を重ね続けている。10nmですら、あのインテルが猛烈に苦戦しているというのに、ここから更に7nm → 5nm → 3nmへと微細化が進むイメージが持てない。

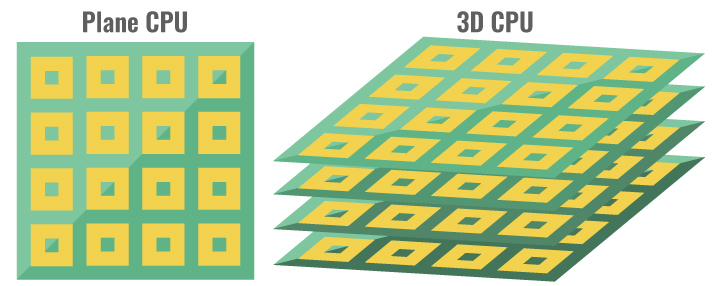

そこでAMDが模索し始めているのが「積層」です。平面への拡張がダメなら、立体に拡張すればいいじゃない。という考え方。ちなみに現在のSSDは積層が使われています。平面では色々と限界があったので。

こんな感じ。これはこれで、どうやって熱を処理するのか、などなど課題は多い。近い将来に実現するつもりは当然なく、遠い将来は3Dの積層構造のCPUが誕生するかも…しれないくらいの状況です。

以上「【CPUの基本】図解でよく分かる「プロセスルール」の意味」でした。

もっと「CPUの基本」を知る

CPUのあるある質問「スレッドとは何なのか?」について、図解してみた記事。

クロック周波数の限界と、その後CPUがどのようにして性能アップを図っていったのかを解説した記事。

おすすめゲーミングPC:7選

おすすめゲーミングPC:7選 ゲーミングモニターおすすめ:7選

ゲーミングモニターおすすめ:7選 【PS5】おすすめゲーミングモニター

【PS5】おすすめゲーミングモニター NEXTGEAR 7800X3Dの実機レビュー

NEXTGEAR 7800X3Dの実機レビュー LEVEL∞の実機レビュー

LEVEL∞の実機レビュー GALLERIAの実機レビュー

GALLERIAの実機レビュー 【予算10万円】自作PCプラン解説

【予算10万円】自作PCプラン解説 おすすめグラボ:7選

おすすめグラボ:7選 おすすめのSSD:10選

おすすめのSSD:10選 おすすめの電源ユニット10選

おすすめの電源ユニット10選

「ドスパラ」でおすすめなゲーミングPC

「ドスパラ」でおすすめなゲーミングPC

やかもちのTwitterアカ

やかもちのTwitterアカ

大変勉強になりました!!

丁度知りたかった内容でしたので神タイミングの記事です。

インテルが10nm製造でうまく行かない理由が何なのか気になりますね。

レーザーの精度なのか、設計が難しいのか・・・

何らかの技術革新でそこが一気に改善すれば良いですね

現行CPUは銅で回路を引いてるけどIntel10nmは新たにコバルトで引こうとした

回路は電子が流れると少なからずダメージを受けるので、それに対し銅より丈夫なコバルトで引くことで微細化しても丈夫な回路を作れるという発想

でもコバルトは銅より電気抵抗が高くてより熱が出てしまい、それを抑えられなかったそうで

Intelの10nmは作り直す以前のものより大人しいとか情報出たこともあるぐらいなんでほんとにTSMCの7nm=Intelの10nmになるのかどうか怪しいんだよな

質問があります

zenの前amdはブルドーザーでボロ糞言われました

ただハイパフォーマンスのFXは32nm

高い内蔵性能が自慢のAPUでも28nm

で微細化が止まりました

もしもっと微細化出来てたらここまで

言われることは無かったののでしょうか?

Bulldozer系CPUの最大の問題点はクロックあたりの処理能力が低いことでした

IntelCPUの4GHzにシングルスレッド性能で対抗するには6〜7GHz程度が必要だったにもかかわらずクロックはそれほど大きく上げられるわけではないので残念な代物になってしまいました

なのでこれは微細化して良くなるというものではないです。同程度のクロックであれば消費電力の軽減は期待できるかもしれませんがその程度です。根本的な性能の低さは微細化しただけではどうにもなりません

いつも読みやすく勉強させて頂いてます。以前の【CPUの基本】図解でよくわかる「マルチコア / スレッド」の意味も合わせて読みながら悩んでいます。スマホなのですがiPhoneSEか同じ価格帯でAndroidにするかです。動画ダウンロードが主な使用用途です。現在約30000円です。SE は小型が気に入ってます、そして最後の購入チャンスです。このような用途の場合、やかもちさんはどちらが向いていると判断されますか?アドバイスをいただきたくコメントしました。宜しくお願い致します。

30000円の予算なら、新品のAndroidでも良いと思います。

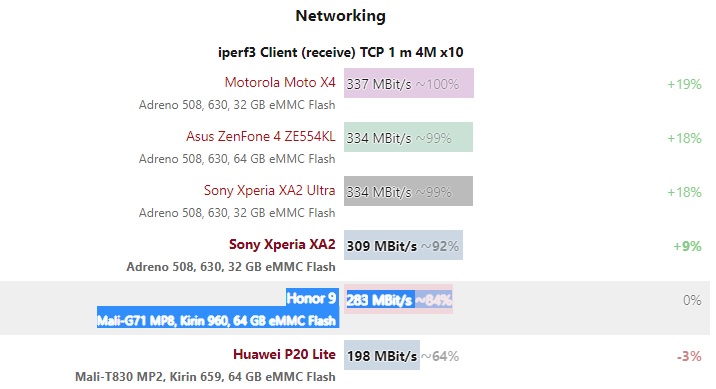

「Huawei P20 Lite」「Oppo R15 Neo」「Huawei Honor 9(中古)」といった、コスパに優れたSIMフリースマホがあります。

新しいスマホの方が、インターネットの接続速度も速い傾向にあるので、ダウンロードが目的ならネットが速いスマホの方が有利だと考えています。

ちなみに、海外のベンチマークを見たところ、先に挙げた3機種の中で「Honor 9」がもっとも通信が速いようです。

ご丁寧なアドバイスありがとうございます。私はスマホ、PC に興味を持って2年目の初心者です。これからも楽しく読ませて頂きたいと思います。

相変わらずレベルが高い

後藤(弘茂)さんレベルの情報量

プロ級。

てっきりシリコンウェハ上に極省のトランジスタを張り付けてるもんだとおもったら

書いてたんですね(´・ω・`)中々勉強になりもうした

イメージとしては「印刷」に近いですね。配線パターンをシリコンウェハー上に印刷(=露光)して、露光した部分だけに反応する光(=紫外線)をあてて配線を実装しています。

このあたりの詳しい話は富士通による解説が分かりやすいので、参考にどうぞ。

もう少しだけ解説を付け加えると、最近のCPUは「印刷 → 光をあてて配線を浮き彫り」という工程を何度か繰り返す「マルチパターニング」という手法で、更に複雑な配線や、デザインを改善したトランジスタを実装したりしています。3Dプリンターに似た感じです。

印刷ですか…なるほど リンク先も興味深くよめました(*´ω`)

技術の進歩はほんとすごいですこの先さらにどうなるかが楽しみです

ありがとうございました。

すーっごくわかりやすかったです

惜しい、ここまで丁寧に書いてる故に逆に惜しい。

プロセスの細かさの説明としてはレーザー鉛筆は素晴らしい発想だけど、

シリコンの回路形成は、鉛筆で書く、ではなく、写真技術。

レーザープリンタの原理に近い。

(トナーが乗っている場所が必要か、乗ってない場所が必要かが逆)

(トナーを溶かす定着部分とレーザー露光が同じ意味になる。)

最近は光源にレーザー使っているけど、面照射で焼き付けです、誤解の元かと。

後、露光はレーザー当てる行為の事、光に晒すので露光。マスキングは露光じゃないです。

この辺は追記した方が正しい知識になって良いかと。

いやイメージの話なのに正しいもクソもないでしょなにが惜しいだよ偉そうに

イメージの話で間違ってる部分があるって話を理解出来ない位頭がアレな人ですか?

iqの低いお方は例え話が理解出来ないんですよね(笑)

スパコンの記事も将来的に作ってほしいな。CPU・GPU・メモリを中心的に。

安定と信頼のintel持ち上げでいっそスッキリする

えっと、amdが模索しているらしい3D化なんだけど、

一番上だけ普通のcpuにしてその下にTDP5wとかのをつければ良いんじゃないかな

(なんか違うなあ…)

いつも分かりやすい記事にお世話になってます、余所の記事で拝見した情報なのですが、28nmプロセス以下だと消費電力が下がるスケーリング則が通用しない、上手くいかないとの事でいわゆる発熱問題(ダークシリコン)が厳しいイメージがあります。故に微細化よるメリットは厳しい印象があります。この辺りの問題が上手くいくことを望んでます。

いつも動画を拝見しております。

「PS5でAMDの7nmのGPUを採用」という記事を読んで

『7nmって何のサイズだろう?なにが凄いんだろう?』

と思っていたところ、この記事でしっかり理解できました。

死ぬほど分かりやすい例えや図もいれて初心者にも優しい解説が好きです。

こんな感じで色々教えてください!

[…] 【CPUの基本】図解でよく分かる「プロセスルール」の意味 […]

7nmというワードがよく出て来るものの意味がわからず、調べてみましたらいつも楽しく読ませていただいているこのサイトのページに辿り着きました。

とてもよく分かりました。いつもありがとうございます。

[…] 【CPUの基本】図解でよく分かる「プロセスルール」の意味 ちもろぐさんに飛びます […]

[…] >>51 https://chimolog.co/bto-cpu-process/ ちょっと簡略化しすぎてて語弊があるけど初心者にもわかりやすく書かれている記事だ とりあえずこいつを読んでみてくれ それでもわからなけり […]

先生!鉛筆よりもシャープペンの芯やボールペンに例えた方が、直感的にイメージしやすかったかも!

一般的に鉛筆は「太さ」で分類されておらず、「濃さ」で分類されています!

対してシャープペンの芯やボールペンは、「太さ」で分類されています!

したがって、直感的にイメージしやすいのは後者だと、私は思います!

解説中にもボールペンに例えられている部分があるのに、何故に鉛筆で例え続けているのか、疑問に思ってしまいますた!(“`д´)ゞ

それ

解りやすかったです。

有難う御座いました。

[…] のプロセスルールが28nmから12nmに改良されたことで、処理性能を上げつつ消費電力削減も達成。 […]

[…] 【CPUの基本】図解でよく分かる「プロセスルール」の意味半導体産業について調べています。整体ネタはほぼなし。なんでそんなことを調べたかというと、台湾海峡問題のリスクが高まっているからです。現在世界で最先端の半導体工場(ファウンドリー)を持つのは、台湾です。TSMCですね。私のRyzenもそのうちTSMC7nmか6nmの新世代に交換予定です。 […]

[…] 参考:【CPUの基本】図解でよく分かる「プロセスルール」の意味 […]

今や3nmで来年のスマホには2nmが搭載されるといわれている、、